# Two Step Dimmable Isolated AC/DC LED Driver

#### **Features**

- Constant current LED driver

- Primary side regulation without photocoupler

- Built-in active power factor correction

- Quasi-resonant switching

- Universal input voltage range

- Support up to 50W output

- Full protections: Thermal shutdown

V<sub>DD</sub> over voltage (OVP)

Under voltage lock-out (UVLO)

LED open-/short- circuit

Current sensing resistor open/short-circuit

Compensating capacitor open/short-circuit

- Available in SOP-8 package

- 2 steps dimmable by input voltage toggling

- High 2<sup>nd</sup> step output current accuracy

- Package MSL Level: 3

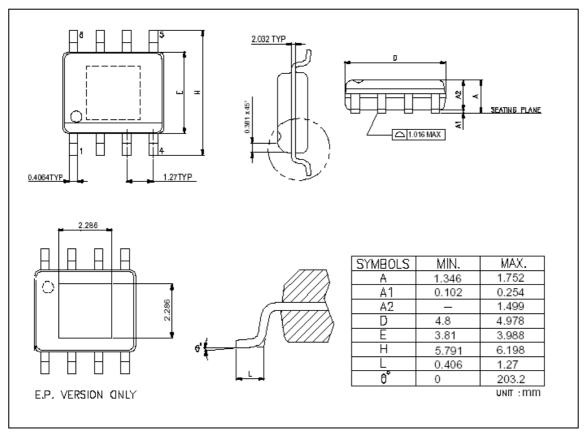

# Small Outline Package GD: SOP8-150-1.27

# **Product Description**

MBI6804 is a universal input AC-DC converter designed to deliver constant current with primary side regulation (PSR) control. The built-in active power factor correction circuit maintains high power factor over a wide input voltage range. MBI6804 is optimized for applications of output power up to 50 Watt, and the efficiency is enhanced with quasi-resonant switching technique. MBI6804 is also featured with under voltage lock-out (UVLO), over temperature protection (OTP), LED open-circuit protection and LED short-circuit protection to protect the converter from being damaged accidentally. MBI6804 is specifically designed with current sensing resistor short protection to prevent MOSFET over-current and transformer saturation caused by manufacturing defect such as solder splash or abnormal operation such as accidental short-circuit by earthquake.

# **Applications**

- T8 light tube LED alternative solutions

- E26/E27 light bulb LED alternative solutions

- PAR light LED alternative solutions

- External LED power supply

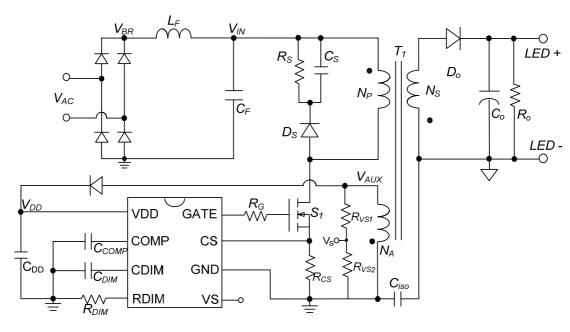

# Typical Application Circuit

Fig.1 Typical application circuit of MBI6804

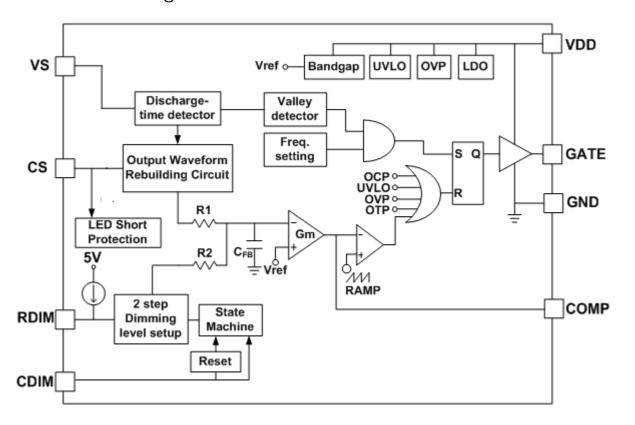

## **Functional Diagram**

Fig.2 Functional diagram of MBI6804

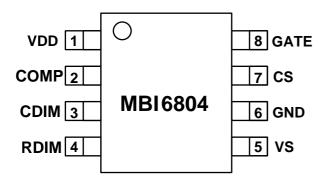

# Pin Configuration

Fig. 3 Pin configuration of MBI6804

# Pin Description

| Pin  | Number | Description                                                              |

|------|--------|--------------------------------------------------------------------------|

| VDD  | 1      | Supply voltage terminal                                                  |

| COMP | 2      | Terminal to connect the compensator                                      |

| CDIM | 3      | Terminal to connect the Cdim capacitor                                   |

| RDIM | 4      | Terminal to connect the Rdim resistor                                    |

| VS   | 5      | Terminal to connect the sensing circuit of the auxiliary winding voltage |

| GND  | 6      | Ground terminal                                                          |

| CS   | 7      | Terminal to connect the MOSFET current sensing resistor                  |

| GATE | 8      | Terminal to connect the gate of the external MOSFET                      |

# **Absolute Maximum Ratings**

NOTE: Operations above the maximum ratings may cause device failure or reduce device reliability.

| Characteristics                                                               |                      | Symbol                             | Min  | Max                | Unit |

|-------------------------------------------------------------------------------|----------------------|------------------------------------|------|--------------------|------|

| Supply voltage                                                                |                      | $V_{DD}$                           | -0.3 | 22                 | V    |

| CS pin input volta                                                            | CS pin input voltage |                                    | -0.3 | 7                  | V    |

| VS pin input voltage                                                          |                      | $V_{VS}$                           | -0.3 | 7                  | V    |

| COMP pin input voltage                                                        |                      | V <sub>COM</sub>                   | -0.3 | 7                  | V    |

| Gate pin output voltage                                                       |                      | $V_{GATE}$                         | -0.3 | 16                 | V    |

| CDIM pin input voltage                                                        |                      | V <sub>CDIM</sub>                  | -0.3 | 7                  | V    |

| RDIM pin input voltage                                                        |                      | $V_{RDIM}$                         | -0.3 | 7                  | V    |

| Junction temperature                                                          |                      | $T_J,MAX$                          | -    | 150**              | °C   |

| Operating ambient temperature                                                 |                      | T <sub>OPR</sub>                   | -40  | 85                 | °C   |

| Storage temperature                                                           |                      | $T_{STG}$                          | -55  | 150                | °C   |

| ESD protection                                                                | Human body mode      | HBM(MIL-STD_833H<br>METHOD 3015.8) | -    | Class 3A<br>(5KV)  | -    |

|                                                                               | Machine mode         | MM(ANSI/ESD<br>S5.2-2009)          | -    | Class M4<br>(450V) | -    |

| Power dissipation                                                             |                      | $P_{D}$                            | -    | 3.13               | W    |

| (On 4 layer PCB, Ta=25°C) Thermal resistance (By simulation, on 4 layer PCB)* |                      | R <sub>th(j-a)</sub>               | -    | 72.1               | °C/W |

<sup>\*</sup>The PCB size is 76.2mm x 114.3mm in simulation. Please refer to JEDEC JESD51.

Note: The performance of thermal dissipation is strongly related to the size of thermal pad, thickness and layer numbers of the PCB. The empirical thermal resistance may be different from simulative value. Users should plan for expected thermal dissipation performance by selecting package and arranging layout of the PCB to maximize the capability.

<sup>\*\*</sup> Operation at the maximum rating for extended periods may reduce the device reliability; therefore, the suggested junction temperature of the device is under 125°C.

# **Electrical Characteristics**

Test condition:  $V_{DD}$ =18V,  $C_{IN}$ =10 $\mu F$ , and  $T_A$ =25°C unless otherwise specified.

| Characteristics                         | Symbol                  | Conditions                                              | Min      | Тур  | Max      | Unit |

|-----------------------------------------|-------------------------|---------------------------------------------------------|----------|------|----------|------|

| Supply Voltage                          |                         |                                                         |          |      |          |      |

| Continuous operating voltage            | V <sub>OP</sub>         | -                                                       | -        | 14   | -        | V    |

| Start-up voltage                        | $V_{START\_UP}$         | Start-up                                                | -        | 17   | -        | V    |

| Under-voltage lockout                   | $V_{UVLO}$              | UVLO                                                    | -        | 7    | -        | V    |

| V <sub>DD</sub> over-voltage protection | $V_{DD\text{-}OVP}$     | -                                                       | 18       | 20   | 22       | V    |

| Operating current                       | I <sub>DD-OP</sub>      | VDD=18V,C <sub>L</sub> =1nF,<br>Fsw=20kHz               | -        | 1.2  | 2        | mA   |

|                                         |                         | VDD=18V,C <sub>L</sub> =1nF,<br>F <sub>SW</sub> =120kHz | -        | 2.5  | 5        | mA   |

| Stand-by current                        | I <sub>DD-ST</sub>      | IDD before start-up                                     | -        | 20   | 30       | uA   |

| Error Amplifier                         |                         |                                                         |          |      |          |      |

| Reference Voltage                       | $V_{REF}$               | -                                                       | 1.176    | 1.2  | 1.224    | V    |

| COMP Pre-charge Voltage                 | $\Delta V_{PC}$         | At first start up                                       | -        | 1.25 | -        | V    |

| COMP Clamping Voltage                   | $V_{CLAMP}$             | -                                                       | -        | 4    | -        | V    |

| Maximum COMP Charging Current           | I <sub>COMP</sub>       | -                                                       | -        | 65   | -        | uA   |

| Current Sense                           | - 1                     |                                                         |          |      | <b>.</b> | · •  |

| Current Limit Threshold Voltage         | $V_{CL}$                | -                                                       | 0.9      | 1    | 1.1      | V    |

| Voltage Sense                           | -1                      |                                                         | <u> </u> |      |          | II.  |

| VS Pin Sourcing Current                 | I <sub>Source_VS</sub>  | VS=-0.3V                                                |          | 8.0  | -        | mA   |

| Gate Driver                             | 1                       |                                                         |          |      |          | II.  |

| Output high voltage                     | V <sub>OH</sub>         | V <sub>DD</sub> =20V<br>at operating                    | -        | 12   | -        | V    |

| Output low voltage                      | V <sub>OL</sub>         | V <sub>DD</sub> =20V<br>at operating                    | -        | -    | 0.5      | V    |

| Rising time                             | T <sub>R</sub>          | V <sub>DD</sub> =20V,<br>20%-80% of swing               | -        | 35   | 70       | ns   |

| Falling time                            | T <sub>F</sub>          | V <sub>DD</sub> =20V,<br>20%-80% of swing               | -        | 25   | 60       | ns   |

| Maximum On-time                         | T <sub>ON_Max</sub>     | COMP=3.8V                                               | -        | 14   | -        | us   |

| Minimum On-time                         | $T_{ON\_min}$           | CS=1.5V                                                 | -        | 200  | -        | ns   |

| Maximum Off-time                        | $T_{OFF\_Max}$          | -                                                       | -        | 50   | -        | us   |

| Maximum Switching Frequency             | F <sub>Switch_Max</sub> | -                                                       | 105      | 120  | 135      | kHz  |

| Thermal Shutdown                        |                         |                                                         |          |      |          |      |

| Thermal shutdown threshold              | T <sub>SD</sub>         | Hysteresis=30 ℃                                         | 140      | 155  | 170      | °C   |

| Dimming                                 |                         |                                                         |          |      |          |      |

| Dimming Step Number                     | -                       | -                                                       | -        | 2    | -        | time |

| Dimming Block Current                   | -                       | -                                                       | -        | 6    | 10       | uA   |

| Dimming Block Hold Time                 | -                       | Сым≦10uF                                                | 1        |      | -        | S    |

| Dimming Block Operating Voltage         | -                       | -                                                       | -        | 4.5  | -        | V    |

| Dimming Reset Voltage                   | -                       | -                                                       | -        | 2.2  | -        | V    |

| Rdim Output Current                     | -                       | -                                                       | -        | 105  | -        | uA   |

## **Application Information**

MBI6804 is a primary side regulator (PSR) optimized for flyback converters. With the primary side regulation technique, the output LED current can be precisely sensed and regulated without any photocoupler. The built-in power factor correction (PFC) circuit maintains high power factor over a wide input voltage range while suppresses the harmonic current to conform to EN61000-3-2 regulations. The embedded quasi-resonant switching technique enables each cycle to start at the relative valley of the drain-source voltage (V<sub>DS</sub>) of the MOSFET, which greatly enhances the conversion efficiency and alleviates radiation EMI. MBI6804 is also equipped with full protections, inclusive of over-temperature protection, LED open-circuit protection, and LED short-circuit protection. The current sensing resistor short protection prevents the damage caused by manufacturing defect or abnormal operation which leads to short-circuit of the current sensing resistor.

## **Operation Principle**

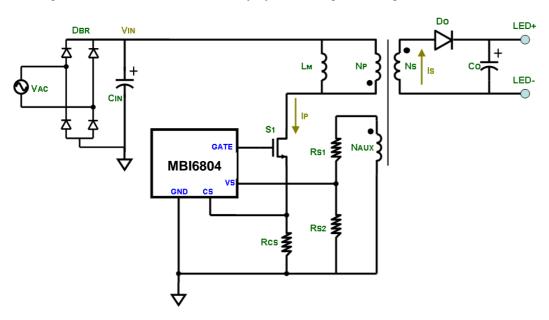

#### **Flyback Converter**

Fig.4 is a simplified diagram of a flyback converter controlled by MBI6804. When  $S_1$  is on, input  $V_{IN}$  charges the magnetizing inductor  $L_{M}$ ; the secondary side is reversely-blocked by  $D_{O}$  and the LED current is supplied by  $C_{O}$ . When  $S_1$  is off, the energy stored on the magnetizing inductor is discharged to the secondary side and therefore supplies the LED current and recharges  $C_{O}$ .

When  $S_1$  is off and  $D_0$  conducts, the output voltage is approximately equal to the voltage across the secondary winding, which can be detected indirectly by measuring the voltage waveform across the auxiliary winding  $N_{AUX}$ .

Fig. 4 Simplified flyback converter controlled by MBI6804

#### **Primary Side Regulation**

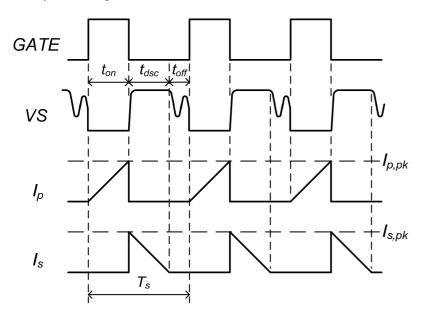

Fig.5 Typical switching waveforms of primary components of a flyback converter

Fig.5 illustrates a typical waveforms of a flyback converter operated in discontinuous conduction mode (DCM), in which  $t_{on}$  is the conduction period of the MOSFET,  $t_{dsc}$  is the conduction period of output diode,  $t_{off}$  is the period in which both MOSFET and the output diode are cut off, and  $T_s$  represents the entire switching period. The signal *GATE* is the control signal of the gate terminal of the MOSFET, and the signal *VS* is the voltage-dividing replica of the auxiliary winding voltage. When the magnetizing inductor is fully discharged, the secondary side current  $I_s$  decreases to zero and *VS* abruptly drops accordingly. By detecting the onset of this voltage drop, the secondary side discharge time  $t_{dsc}$  can be calculated. The average output current  $I_o$  can be mathematically deduced as

$$I_{o} = \frac{1}{2} \cdot \frac{t_{dsc}}{T_{s}} \cdot I_{s, pk}$$

$$= \frac{1}{2} \cdot \frac{t_{dsc}}{T_{s}} \cdot \frac{N_{P}}{N_{S}} \cdot I_{p, pk}$$

$$= \frac{1}{2} \cdot \frac{t_{dsc}}{T_{s}} \cdot \frac{N_{P}}{N_{S}} \cdot \frac{V_{cs, pk}}{R_{cs}}$$

$$(2)$$

The primary side peak current  $I_{p,pk}$  can be directly sensed at pin CS.

#### **Active Power Factor Correction (APFC)**

Theoretically, when the input main voltage and input current are in phase and proportional to each other, the power factor will be unity. In a flyback converter, this is equivalent to the proportionality between the voltage across the magnetizing inductor  $V_{LM}$  and the average current of the primary side  $I_{P(avg)}$ , both of which are also proportional to the peak value of the magnetizing inductor current  $I_{LM(peak)}$ , as stated in equations (4) and (5).

$$V_{LM} \propto I_{P(avg)} \begin{cases} V_{LM} \propto I_{LM(peak)} \dots (4) \\ I_{LM(peak)} \propto I_{P(avg)} \dots (5) \end{cases}$$

For a flyback converter, if the conduction period  $t_{on}$  and the magnetizing inductance  $L_M$  are fixed, equation (4) will stand for reason according to equation (6) regardless of operations in either DCM or BCM. Meanwhile, based on equation (7),  $D_{on}$  has to be kept constant, which in turns indicates the period of the switching cycle  $T_S$  must also be kept constant. Therefore, variations of  $L_M$ ,  $t_{on}$ ,  $D_{on}$ , and  $T_S$  must be small in order to obtain a high PF design.

$$V_{LM} = L_M \frac{I_{LM(peak)}}{t_{co}} \tag{6}$$

$$I_{P(avg)} = \frac{1}{2} \frac{I_{LM(peak)} t_{on}}{T_{s}} = \frac{1}{2} \frac{I_{LM(peak)} D_{on} T_{s}}{T_{s}} = \frac{1}{2} I_{LM(peak)} D_{on} \dots (7)$$

If the transformer is properly designed, the magnetizing inductance  $L_M$  should be constant without core saturation. By adjusting the system response to be slower than the input line frequency,  $t_{ON}$  can be kept relatively constant for several line cycles. Besides, an operation in DCM indicates a fixed-frequency operation, which means  $T_S$  and  $D_{ON}$  will be constant and therefore a high power factor can be achieved. On the other hand, BCM is an inherent variable-frequency operation in nature; therefore  $T_S$  and  $D_{ON}$  will not be constant and achievable power factor is relatively low.

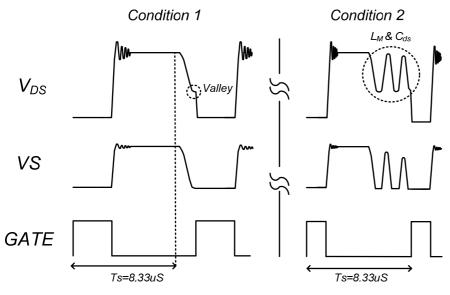

#### Quasi-Resonant (QR) Switching

Fig. 6 illustrates typical switching waveforms of a quasi-resonant flyback converter. When the magnetizing inductor is fully discharged, the residue charge on the MOSFET parasitic capacitance  $C_{ds}$  induces a resonant between the magnetizing inductor  $L_M$  and  $C_{ds}$ . As illustrated in *Condition 1*, MBI6804 detects the first valley of the resonant response and turns on the MOSFET to initiate the very next switching cycle. In some applications, as depicted in *Condition 2*, the MOSFET is turned on at another relative valley of the resonant due to minimum switching period limitation (8.33 $\mu$ s, or equivalently 120kHz maximum switching frequency). In both cases, the switching loss is minimized and the radiation EMI is alleviated because to the onset of each switching cycle is at the voltage valley.

Fig.6 Typical quasi-resonant switching waveforms of MBI6804

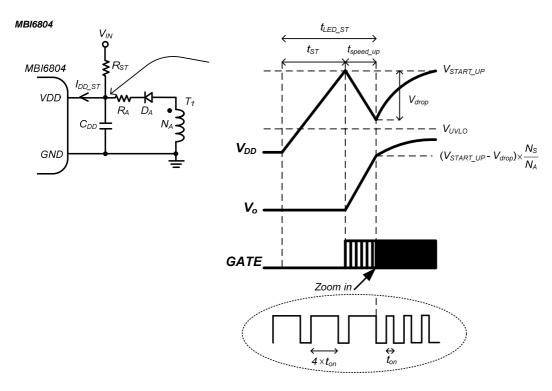

#### Start-Up

Upon system power-on, the input voltage  $V_{IN}$  charges capacitor  $C_{DD}$  through resistor  $R_{ST}$  with start-up current  $I_{DD\_ST}$ . Once  $V_{DD}$  reaches start-up threshold  $V_{DD\_ON}$ ,MBI6804 starts normal operation with quiescent current  $I_{DD\_NORMAL}$ . Before the output voltage  $V_o$  is fully established, the chip power consumption of MBI6804 is solely supplied by the capacitor  $C_{DD}$ . As depicted in Fig. 7, the built-in speedup circuit shortens the start-up time by quadrupling the conduction period of the MOSFET within the pre-defined  $t_{speed\_up}$ .

Fig. 7 Typical start-up waveforms of MBI6804

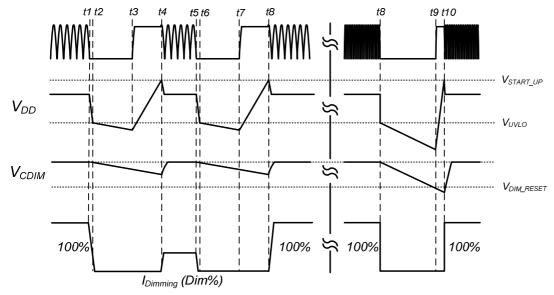

#### **Dimming Methodology**

The dimming method can be described simply as the combination of the following actions.

Fig.8 Dimming method of MBI6804

- 1. t1= power-off started

- 2. t2= V<sub>DD</sub> drops below UVLO 6.7V, V<sub>CDIM</sub> starts to drop. Power-on before it reaches 1.7V, the dimming function can be triggered.

- 3. After power-off, if power-on before VDD reaches UVLO, the output state will not change.

- 4. Power-on after VCDIM drops below 1.7V. The output will reset to 100%.

IRDIM=100uA: VRDIM = IRDIM X RDIM

| VRDIM(V) | Dimming % |

|----------|-----------|

| >4       | 100       |

| 3~4      | 50        |

| 2.5~3    | 45        |

| 2~2.5    | 40        |

| 1.5~2    | 35        |

| 1~1.5    | 30        |

| 0.5~1    | 25        |

| <0.5     | 20        |

#### Protection

#### **V<sub>DD</sub> Over Voltage Protection (OVP)**

The build-in over voltage protection is implemented by VDD pin. When the voltage on VDD exceeds  $V_{DD\_OVP}$  due to the abnormal voltage on auxiliary winding, the GATE signal will stop switching immediately and shut off MBI6804 until the  $V_{DD}$  voltage drops to UVLO.

#### **Under Voltage Lock-Out (UVLO)**

When  $V_{IN}$  drops below 6.5V, the GATE output will be forced low to turn off the external power MOSFET. When  $V_{IN}$  rises above 16.0V, the GATE output resumes normal operation and the external power MOSFET starts switching.

#### **Over Temperature Protection (OTP)**

When the junction temperature exceeds 155°C, the built-in over-temperature protection (OTP) is activated to force off the MOSFET. Once the junction temperature drops below 125°C, OTP is deactivated and MBI6804 resumes normal operation.

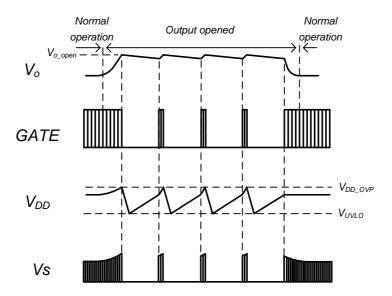

#### **LED Open-Circuit Protection**

The operation of LED open-circuit protection is illustrated in Fig.9. When LED is opened, the voltage on VDD pin rises with the output voltage; once the  $V_{DD}$  voltage achieves the threshold voltage of open circuit protection ( $V_{DD\_OVP}$ ), the GATE signal will stop switching until the  $V_{DD}$  voltage drops to UVLO. When the  $V_{DD}$  drops to UVLO, and then the converter will restart from soft start mode again. The cycle will be repeated until the fault is removed. In general, to prevent IC being damaged by spike voltage, a clamp circuit is paralleled with VDD pin. To ensure IC works normal, the clamp voltage should be designed between the maximum rating of VDD and  $V_{DD\_OVP}$ . The

specification of zener diode, 1SMA4749, from Panjit could be the reference of clamp circuit.

Fig.9 Conceptual waveform of  $V_{O}$ , GATE,  $V_{DD}$  and  $V_{S}$  when output is opened and recovered

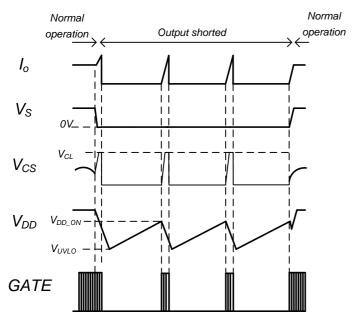

#### **LED Short-Circuit Protection**

The operation of LED short-circuit protection is illustrated in Fig.10 By detecting whether the voltage at pin VS drops to zero while the voltage at pin CS exceeds 1.0V, MBI6804 can judge the occurrence of LED short-circuit failure. Once LED short-circuit failure occurs, GATE signal ceases switching and  $V_{DD}$  drops with the output voltage. The converter is fully turned off when  $V_{DD}$  drop below  $V_{UVLO}$  and the converter automatically restarts. After the system restarts, MBI6804 will shut down the converter again if the short-circuit condition still exists or resume normal operation once the short-circuit condition is removed

Fig. 10 LED short-circuit protection

# MBI6804 Two Step Dimmable Isolated AC/DC LED Driver

#### **Current Sensing Resistor Open/Short Protection**

MBI6804 is designed with current sensing resistor open/short protection to prevent extreme fault conditions from irrecoverably damaging the converter, such as cold welding or solder splash during manufacturing process, and accidental short circuit caused by earthquake or abnormal vibration during normal operations.

#### **Compensating Capacitor Open/Short Protection**

In normal operation without additional protection, floating or short-circuit of the compensating capacitor would lead to unexpected behavior of the internal error amplifier, which primarily guarantee the close-loop stability. MBI6804 specially provides compensating capacitor open/short protection against these fault conditions from destabilizing the converter.

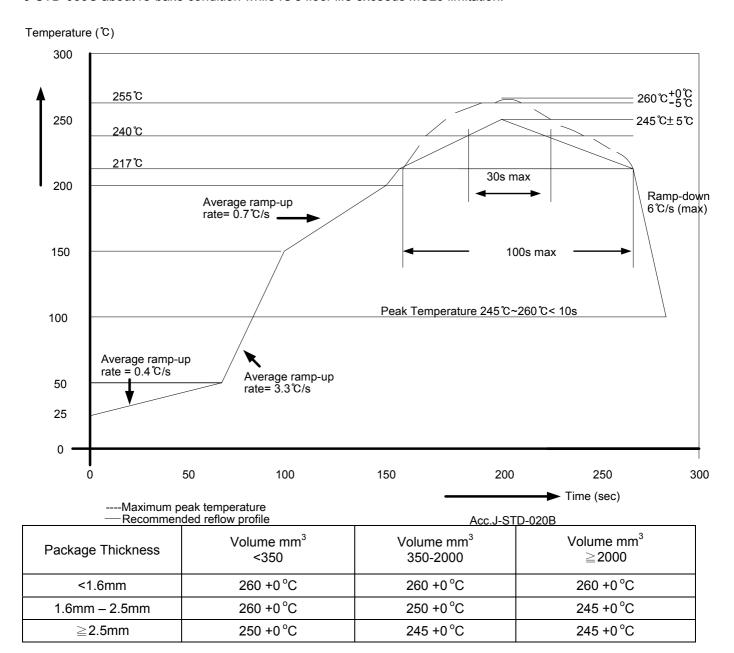

# Soldering Process of "Pb-free & Green" Package Plating\*

Macroblock has defined "Pb-Free & Green" to mean semiconductor products that are compatible with the current RoHS requirements and selected 100% pure tin (Sn) to provide forward and backward compatibility with both the current industry-standard SnPb-based soldering processes and higher-temperature Pb-free processes. Pure tin is widely accepted by customers and suppliers of electronic devices in Europe, Asia and the US as the lead-free surface finish of choice to replace tin-lead. Also, it adopts tin/lead (SnPb) solder paste, and please refer to the JEDEC J-STD-020C for the temperature of solder bath. However, in the whole Pb-free soldering processes and materials, 100% pure tin (Sn) will all require from 245 °C to 260°C for proper soldering on boards, referring to JEDEC J-STD-020C as shown below.

For managing MSL3 Package, it should refer to JEDEC J-STD-020C about floor life management & refer to JEDEC J-STD-033C about re-bake condition while IC's floor life exceeds MSL3 limitation.

<sup>\*</sup>Note: For details, please refer to Macroblock's "Policy on Pb-free & Green Package".

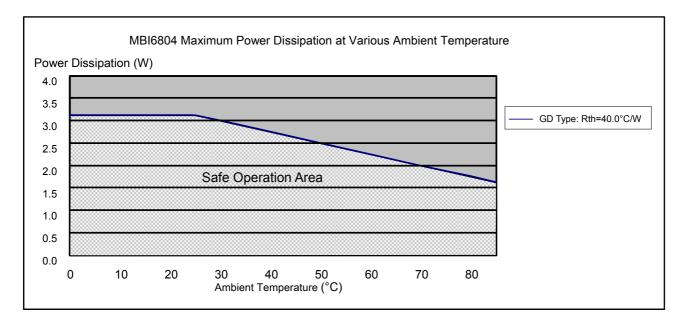

# Package Power Dissipation (PD)

The maximum power dissipation,  $P_D(max)=(Tj-Ta)/R_{th(j-a)}$ , decreases as the ambient temperature increases.

# **Outline Drawings**

MBI6804 GD outline drawing

Note1: The unit for the outline drawing is mm.

Note2: Please use the maximum dimensions for the thermal pad layout. To avoid the short circuit risk, the vias or circuit traces shall not pass through the maximum area of thermal pad.

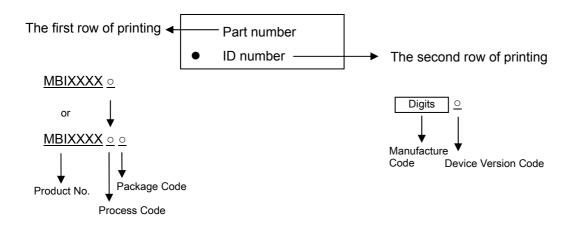

# **Product Top Mark Information**

#### GD(SOP-8)

# **Product Revision History**

| Datasheet version | Device Version Code |  |  |

|-------------------|---------------------|--|--|

| V1.00             | A                   |  |  |

| V2.00             | В                   |  |  |

| V3.00             | С                   |  |  |

# **Product Ordering Information**

| Part Number | "RoHS Compliant" Package Type | Weight (g) |

|-------------|-------------------------------|------------|

| MBI6804GD-C | SOP8-150-1.27                 | 0.079g     |

<sup>\*</sup>Please place your order with the "product ordering number" information on your purchase order (PO).

#### Disclaimer

Macroblock reserves the right to make changes, corrections, modifications, and improvements to their products and documents or discontinue any product or service. Customers are advised to consult their sales representative for the latest product information before ordering. All products are sold subject to the terms and conditions supplied at the time of order acknowledgement, including those pertaining to warranty, patent infringement, and limitation of liability.

Macroblock's products are not designed to be used as components in device intended to support or sustain life or in military applications. Use of Macroblock's products in components intended for surgical implant into the body, or other applications in which failure of Macroblock's products could create a situation where personal death or injury may occur, is not authorized without the express written approval of the Managing Director of Macroblock. Macroblock will not be held liable for any damages or claims resulting from the use of its products in medical and military applications.

All text, images, logos and information contained on this document is the intellectual property of Macroblock. Unauthorized reproduction, duplication, extraction, use or disclosure of the above mentioned intellectual property will be deemed as infringement.